New UVVM functionality: Detection of unexpected interface activity

Marius Elveg?rd

Disiplinleder Digital ?stlandet, Lokasjonsleder Asker, Senior FPGA-utvikler hos Inventas, UVVM SG

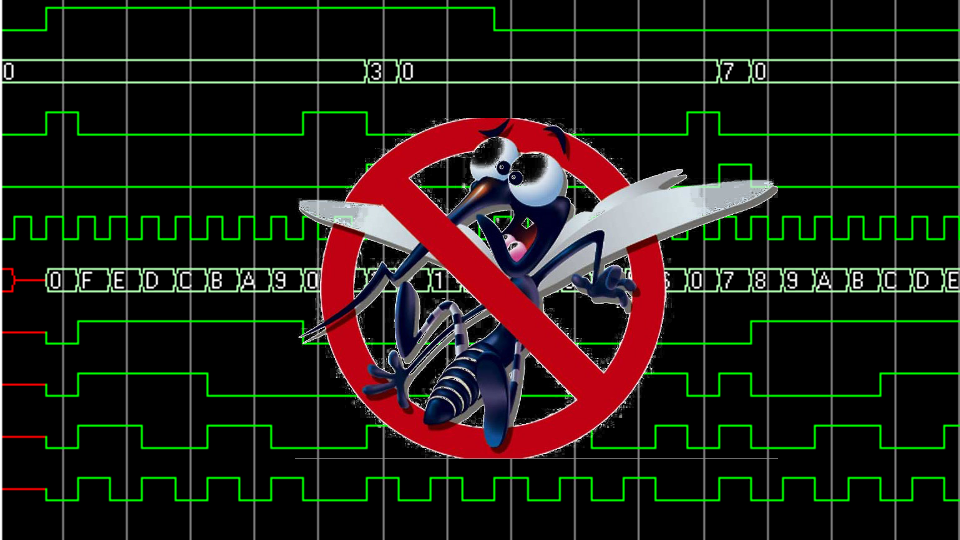

One of the first improvements to come out of the new ESA UVVM project is detection of unexpected activity on a DUT interface. UVVM has provided open source BFMs (Bus Functional Models) and VVCs (VHDL Verification Components) for lots of interfaces - like AXI, AXI-stream, AXI-light, SPI, UART, SBI, Ethernet, GMII, GPIO, Avalon MM, Avalon stream, etc. - for a long time. These have provided excellent access mechanisms for transaction modelling, but also various support for protocol checking. Normal BFMs and VVCs have the limitation though, that they only initiate a transaction or wait for one to occurr. They do not check whether the DUT is only transmitting data when expected.

UVVM now introduces detection of any unwanted or unexpected transactions from the DUT. In fact, UVVM will now detect any unwanted or unexpected activity on a given interface. This new checker may of course be turned on and off from the test sequencer.

We expect this new functionality to be published in June.

As we mentioned in our previous post about the updates in the new ESA-UVVM project, we are now excited to share information about the first new feature: detection of unintended activity on communication lines. In some cases, data can be sent out of a DUT (Device Under Test) unexpectedly, often due to a design error, and we often have no easy way to detect this. A testbench usually focuses on verifying the functional correctness of the design and the accuracy of the data sent from the DUT using the available interface for sending or receiving transfers to and from the DUT. During the intervals between these actions, the DUT interface is not monitored by the testbench, and it requires manual effort to observe if the DUT mistakenly generates noise on the lines or sends unexpected data. The new UVVM extension enhances the VVCs by adding a mechanism to automatically detect unwanted or unexpected transmissions from the DUT. This detection mechanism is configurable in the usual UVVM way and can be controlled from the testbench.

UVVM is an open-source verification tool developed by the VHDL community and sponsored by leading industry actors.

领英推荐

#FPGA #ASIC #UVVM #VERIFICATION #EMBEDDED Inventas