Memory Solutions for Space: Overcoming Radiation Challenges

Gabriel A. Sanca

Passionate about space technology | Small satellite research at UNSAM | LabOSat team member

In the context of space exploration, where the boundaries of technology are continually pushed to their limits, reliable memory solutions play a pivotal role. As humanity ventures further into the cosmos, the demand for robust electronic memory systems capable of withstanding the harsh conditions of space becomes increasingly urgent.

This article delves into the intricate world of memory solutions tailored for space applications, focusing particularly on the formidable challenge posed by ionizing radiation. Drawing from the insights and research from the domain of semiconductor engineering, as well as the exploration of advanced memory technologies, we aim to unravel the complexities surrounding the development of memory systems fit for space missions.

Join us on a journey through the cosmos of memory solutions for space, where innovation meets the rigors of radiation, and where the quest for reliability knows no bounds.

Electronic memories, omnipresent in our daily lives, are at the forefront of technological evolution. From cherished holiday photographs to vital industry data, each bit holds significance. The escalating volume of information handled today propels the semiconductor and nanomaterials industry to seek the "ultimate memory". This kind of universal memory, if it exists, must be dense, fast, energy-efficient, cost-effective, and be non-volatile memory (NVM). It could replace dense storage systems (such as hard disks), as well as every memory hierarchy we have in a computer system, from caches to RAM.

In the space industry, memory emerges as a critical system, not merely due to its data capacity, which continually needs to expand with new applications, but primarily for its resilience in the face of the hostile space environment. Understanding the impact of radiation on memory integrity and devising effective mitigation strategies are imperative for the success of space missions. Diverse memory types, including volatile (SRAM, DRAM) and non-volatile (NAND, NOR flash) memories, each with unique advantages and challenges, serve different functions in memory systems. Emerging technologies such as FRAM [1], CBRAM [2], MRAM [3], and RRAM [4] present promising alternatives, bringing innovation to the forefront of space applications.

In the realm of memory solutions for space, three broad groups come to light: radiation-resistant memories, COTS-based solutions, and emerging technologies. Each group harbors its advantages and drawbacks, ranging from component availability to cost considerations. Among these, the utilization of Commercial Off-The-Shelf components in space [5], emerges as a pivotal strategy to render solid-state mass memory solutions economically viable. COTS components bridge the technological gap and mitigate the exorbitant costs (but remember, the use of COTS is not so cost-effective either!) associated with space-qualified alternatives, and guarantee availability, ensuring that space missions remain both economically viable and technologically robust.

Not only in space exploration, but also in other harsh environments like nuclear accelerators or avionics, the utilization of COTS components emerges as a critical strategy to render solid-state mass memory solutions economically feasible. Cardarilli [5] underscores the significance of adopting COTS components to overcome the technological gap and exorbitant costs associated with space-qualified components. The inherent challenges posed by the space environment necessitate memory solutions that can withstand mechanical stresses, ionizing radiations, and extreme thermal conditions. While space-qualified electronic devices are designed for resilience in such environments, they come with drawbacks such as high costs, performance limitations, and market availability compared to their commercial counterparts. By leveraging COTS components, engineers and designers can bridge the gap between technological requirements and cost-effectiveness, ensuring that space missions remain economically viable without compromising on reliability or performance. As we have previously discussed in BTC, the adoption of COTS components opens avenues for innovation, scalability, and adaptability in space in general, and in the design and implementation of memory solutions, ensuring that the boundaries of exploration are continually pushed forward within sustainable economic parameters.

The advancement of CMOS technology has facilitated a notable reduction in the area per bit within solid-state memories. For instance, the advent of the 90 nm technology node in 2002 enabled the design of SRAMs with a mere 1 μm2 per bit [6], with subsequent generations witnessing a consistent trend of diminishing area. By 2020, the introduction of the 5 nm technology node has further refined this trend, allowing for the development of SRAM cells as small as 0.021 μm2 [7]. However, the escalating level of integration in CMOS memory poses novel challenges when deploying these technologies in space environments, chiefly attributable to the effects induced by multiple bit upsets (MBU) [8, 9].

Concomitant with the downsizing of CMOS technology dimensions, the capacities of the circuit's nodes have undergone significant reduction. Consequently, there exists a diminished critical charge necessary to incite a Single Event Upset (SEU). As a result, modern integrated circuits exhibit heightened sensitivity to particles with lower Linear Energy Transfer (LET). Against this backdrop, and amidst a burgeoning space industry, the rationale for embracing emerging technologies becomes increasingly compelling. These nascent technologies are grounded in diverse material compositions and physical principles. While many of these memory solutions have yet to achieve maturity levels requisite for prototyping, let alone integration into critical systems, the evolving demands of the space sector necessitate the advent of dense and resilient memory technologies. The envisaged challenges confronting the space industry, spanning from deep space exploration to celestial body colonization, underscore the imperative for robust memory solutions. Additionally, the flourishing development of Earth observation and communication technologies amplifies the call for enhanced storage capacities, rendering our current memory paradigms potentially inadequate for future demands.

Within the domain of prototypical memories outlined in the International Roadmap for Devices and Systems (IRDS?) 2023 [10], emerging technologies like RRAMs have garnered significant attention. These technologies, once categorized as emerging a decade ago, exhibit promising characteristics, particularly in their resilience to ionizing radiation and their solid-state nature, which ensures high-speed performance and eliminates mechanical components. This group also includes FRAMs, which are commonly used in space environments [11]. Despite their potential suitability for space applications, it's noteworthy that discussions surrounding the integration of emerging memory technologies into space systems have persisted for years. In 2012, M. Marinella highlighted the prospect of these technologies as viable candidates for space utilization [12]. However, fourteen years later, their widespread adoption in space endeavors has yet to materialize. The question, "Will emerging memory technology reach space?" prompts a nuanced analysis that not only scrutinizes the semiconductor industry's trajectory but also probes the adaptability of the NewSpace sector in reshaping conventional paradigms within integrated circuit manufacturing. Central to this inquiry is the consideration of whether the burgeoning demand within the space market could catalyze the development of specialized chips tailored for space applications on a large scale. Such a shift in dynamics holds implications not only for the aerospace sector but also for adjacent industries like defense, nuclear, and research, which may witness ripple effects from the evolving landscape of space technology integration.

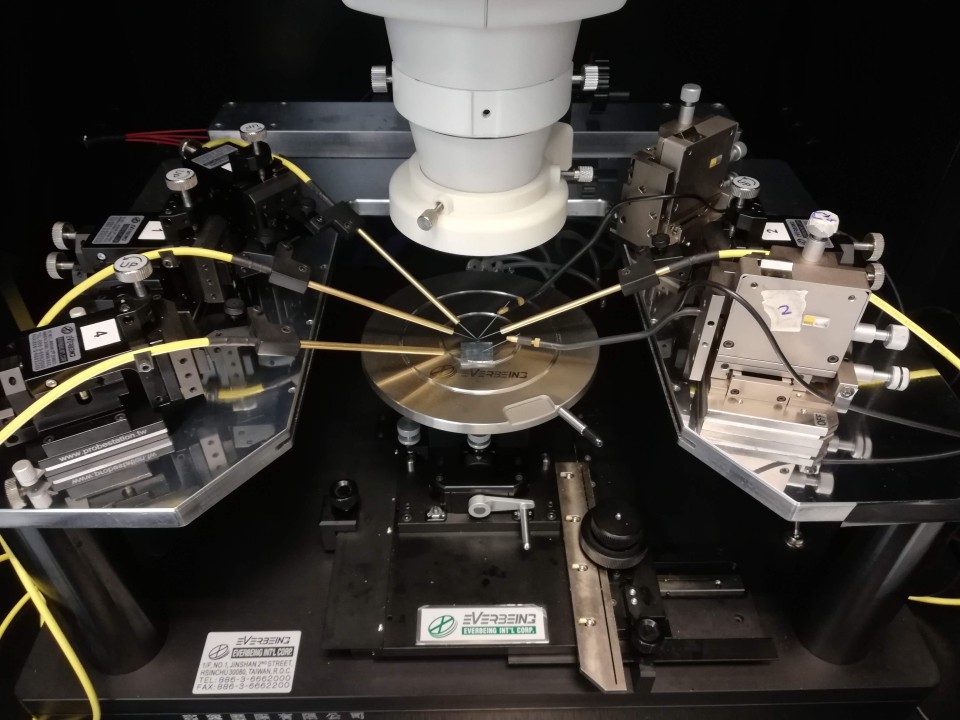

At this juncture, it is imperative to delineate the issue into two distinct aspects. Firstly, the emerging or prototype technologies have yet to attain the status of commercially viable products. This delay primarily stems from technology-specific challenges and, predominantly, the sustained dominance of CMOS technologies. Consequently, these technologies have not garnered adoption within the space industry owing to their absence from the semiconductor industry's offerings. Nonetheless, our understanding of these technologies, particularly their data retention capabilities in adverse environments characterized by ionizing radiation, remains substantial. For example, the adoption of RRAMs as non-volatile memory solutions to challenge CMOS technologies is being actively pursued by various companies, including Crossbar Inc , 4DS Memory , and Panasonic. Notably, Panasonic introduced the MN101L series of microcontrollers featuring integrated RRAMs a few years ago. Through firsthand experience, I have observed the remarkable resilience of these technologies to radiation during extensive testing conducted both on Earth [13] and in orbital environments [14,15]. While significant challenges persist in implementing dense systems utilizing RRAMs, their potential to emerge as resilient and viable memory solutions for space applications is considerable.

The future of space exploration will require robust, dense and affordable memories. The solution to this problem may not be unique, and may need to be approached from several angles. COTS components, but also emerging technologies, will be needed in this new phase. It will be prudent to observe how the NewSpace sector dialogue with the semiconductor industry to foster the development of expansive technologies tailored to meet the demands of the burgeoning and influential space market.

References

[1] Bailey, R., Fox, G., Eliason, J., Depner, M., Kim, D., Jabillo, E., ... & Gertas, J. (2005, October). FRAM memory technology-advantages for low power, fast write, high endurance applications. In 2005 International Conference on Computer Design (pp. 485-485). IEEE Computer Society.

领英推荐

[2] Abbas, H., Li, J., & Ang, D. S. (2022). Conductive bridge random access memory (CBRAM): Challenges and opportunities for memory and neuromorphic computing applications. Micromachines, 13(5), 725.

[3] Bhatti, S., Sbiaa, R., Hirohata, A., Ohno, H., Fukami, S., & Piramanayagam, S. N. (2017). Spintronics based random access memory: a review. Materials Today, 20(9), 530-548.

[4] Zahoor, F., Azni Zulkifli, T. Z., & Khanday, F. A. (2020). Resistive random access memory (RRAM): an overview of materials, switching mechanism, performance, multilevel cell (MLC) storage, modeling, and applications. Nanoscale research letters, 15, 1-26.

[5] Cardarilli, G. C., Ottavi, M., Pontarelli, S., Re, M., & Salsano, A. (2005). Fault tolerant solid state mass memory for space applications. IEEE Transactions on Aerospace and Electronic Systems, 41(4), 1353-1372.

[6] Thompson, S., Anand, N., Armstrong, M., Auth, C., Arcot, B., Alavi, M., ... & Bohr, M. (2002, December). A 90 nm logic technology featuring 50 nm strained silicon channel transistors, 7 layers of Cu interconnects, low k ILD, and 1/spl mu/m/sup 2/SRAM cell. In Digest. International Electron Devices Meeting, (pp. 61-64). IEEE.

[7] Chang, J., Chen, Y-H., Chan, G., Cheng, H., ... & Li, Q. (2020). 15.1 A 5nm 135Mb SRAM in EUV and High-MobilityChannel FinFET Technology with Metal Coupling and Charge-Sharing WriteAssist Circuitry Schemes for High-Density and Low-VMIN Applications. IEEE International Solid- State Circuits Conference - (ISSCC). IEEE,

[8] Ramezani, R., Clemente, J. A., & Franco, F. J. (2020). Analytical reliability estimation of SRAM-based FPGA designs against single-bit and multiple-cell upsets. Reliability Engineering & System Safety, 202, 107036.

[9] Yoshimoto, S., Amashita, T., Okumura, S., Kawaguchi, H., & Yoshimoto, M. (2012). Multiple-bit-upset and single-bit-upset resilient 8T SRAM bitcell layout with divided wordline structure. IEICE transactions on electronics, 95(10), 1675-1681.

[10] International Roadmap for Devices and Systems (IRDS?) 2023 Update

[11] Sansoè, C., & Tranchero, M. (2011). Use of FRAM memories in Spacecrafts. Ferroelectrics-Applications, 213-230.

[12] Marinella, M. (2013, March). The future of memory. In 2013 IEEE Aerospace Conference (pp. 1-11). IEEE.

[13] Acha, C., Sanca, G. A., Barella, M., Alurralde, M., Marlasca, F. G., Huhtinen, H., ... & Levy, P. (2021). Proton irradiation effects on metal-YBCO interfaces. Radiation Physics and Chemistry, 183, 109404.

[14] Barella, M., Sanca, G., Marlasca, F. G., Acevedo, W. R., Rubi, D., Inza, M. G., ... & Golmar, F. (2019). Studying ReRAM devices at low earth orbits using the labosat platform. Radiation Physics and Chemistry, 154, 85-90.

[15] Acha, C., Barella, M., Sanca, G. A., Gomez Marlasca, F., Huhtinen, H., Paturi, P., ... & Golmar, F. (2020). YBCO-based non-volatile ReRAM tested in Low Earth Orbit. Journal of Materials Science: Materials in Electronics, 31, 16389-16397.